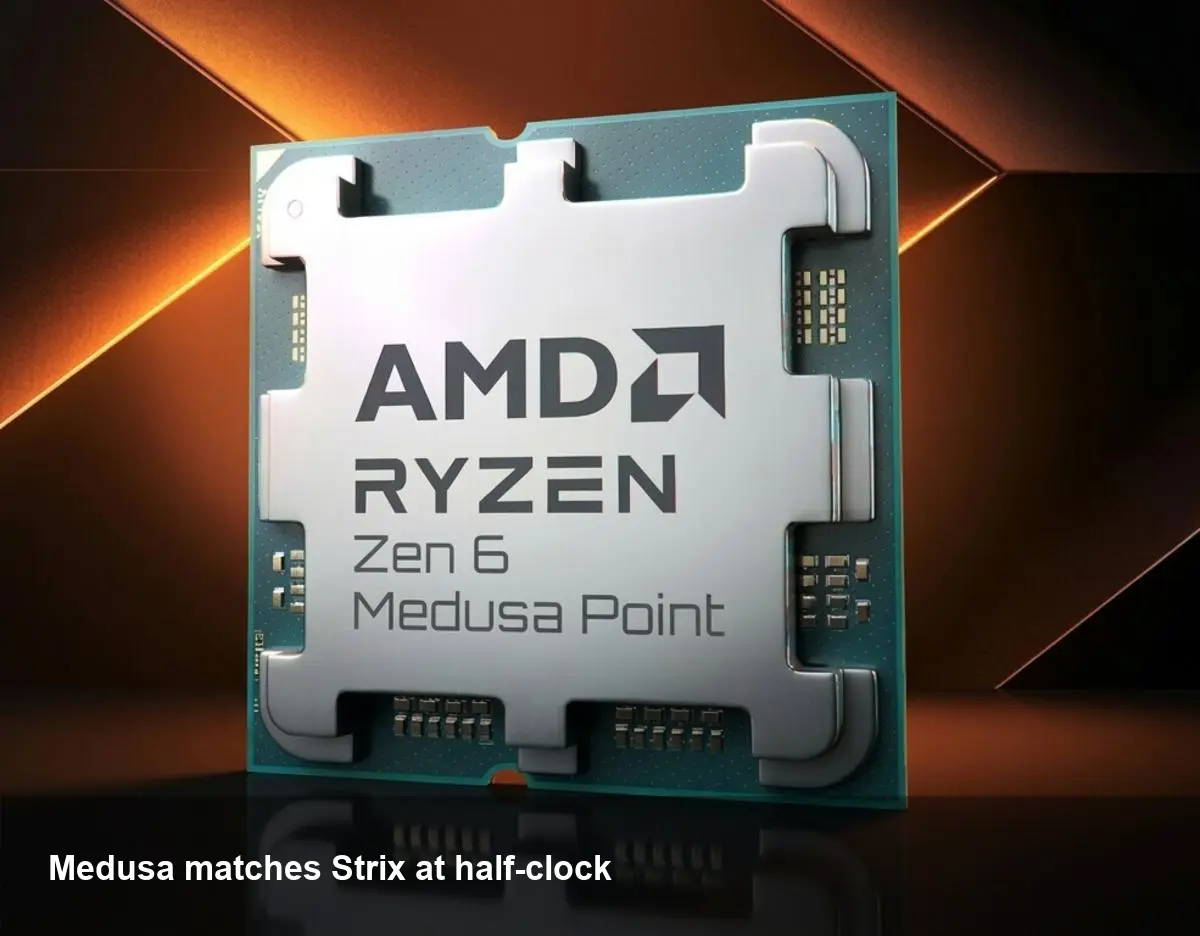

Medusa Point APU: Strix Point Performance at Half Clock

What just surfaced and why it matters

Shortly after engineering samples of AMD's new Medusa Point APU showed up in online benchmarks, the noise started: a 10-core, 20-thread Zen 6 part is scoring similarly to AMD’s existing Strix Point platform while running at roughly half the clock speed. Those results—captured in an early Geekbench v6 entry—aren’t marketing copy. If they hold up on production silicon, they point to significant per-clock (IPC) improvements and a meaningful reshaping of mobile and thin-and-light CPU design.

Quick background: the pieces in play

AMD has continued evolving its Zen architecture family; Zen 6 is the next step and Medusa Point is AMD’s upcoming APU design that pairs Zen 6 CPU cores with integrated graphics in a single system-on-chip. Strix Point is the more established platform AMD has been shipping in some systems. The Medusa Point samples in Geekbench were reported as 10-core/20-thread engineering chips, and AMD expects product launches around early 2027, with OEM partners already testing hardware in labs.

APU here is important: unlike discrete CPUs, APUs combine CPU and GPU on the same die, which is crucial for ultraportables and power-constrained devices that need capable integrated graphics without a discrete GPU.

The headline: similar scores at half the clock

The basic takeaway from the leaked run is simple: Medusa Point produced benchmark numbers in the same neighborhood as Strix Point while running at significantly lower clock speeds. On paper that implies two things:

- Zen 6 delivers noticeably better IPC (work per clock) across workloads.

- For any fixed performance target, the new chip can hit it at a lower frequency—translating to better energy efficiency and lower thermals.

This isn’t just about bragging rights. Performance-per-watt is the metric OEMs and laptop designers care most about when balancing battery life, cooling hardware, and chassis thinness.

Practical scenarios where this changes the user experience

- Thin-and-light laptops: Imagine a 13–14" ultraportable achieving the same multi-threaded editing or compiling speed as today’s thicker models, but with improved battery life and cooler chassis. OEMs could either extend battery runtime or chase higher sustained clocks with the same thermal budget.

- On-the-go developers: Local builds and containerized workflows become more viable on battery. If compile times hold steady while frequencies are reduced, cold-room desks and co-working spaces will see cooler devices and fewer noisy fans.

- Creators and light editors: Video transcodes and photo exports on laptops without discrete GPUs will finish faster or consume less energy—meaning longer editing sessions away from a power outlet.

- Enterprise fleet management: IT fleets can benefit from devices that need less active cooling and have improved battery longevity, reducing operational costs for charging infrastructure and cooling-related support tickets.

What this means for software and developers

Higher IPC at lower clocks changes optimization trade-offs:

- Local testing vs. cloud: More compute becomes feasible on-device, which can reduce cloud costs for developers doing local model inference or dataset filtering before pushing to CI/CD.

- Thermal-aware development: Apps that perform heavy background CPU work (indexing, large-codebase tooling, CI agents) can leverage background scheduling policies to run more efficiently on Medusa-style hardware.

- Compiler and runtime tuning: JITs and compilers could aggressively lean on single-thread IPC improvements for latency-sensitive paths, or tune thread counts differently knowing each core delivers more work at lower clocks.

Caveats and reasons for caution

- Engineering sample vs retail silicon: Early samples often run with reduced frequencies or unfinished firmware. Final silicon, power management firmware, and driver stacks will influence real-world results.

- Single-benchmark snapshot: Geekbench is useful but limited. Full evaluations—Sustained multi-thread tests, real-world apps (compiles, games, encoding), and GPU tests—are still needed.

- Integrated GPU performance unknown: As an APU, the GPU side matters. If AMD focused most gains on CPU IPC while leaving the integrated graphics relatively unchanged, some gaming or GPU-accelerated workloads might not see proportional improvements.

Business and competitive implications

- OEM differentiation: Manufacturers can create thinner, lighter designs or re-balance price tiers—offering higher battery endurance at similar performance points or more performance in thermally constrained designs.

- Pressure on rivals: If Zen 6 delivers the IPC improvements implied here, Intel and other competitors will need to respond across both laptop and mobile segments, not just raw clock wars.

- Opportunity for software vendors: Tools that optimize for energy-efficient execution, like low-power background processing or adaptive framerate managers, become more attractive as hardware supports stronger performance-per-watt.

Three forward-looking insights

- IPC-first architectures reduce the value of clock-speed marketing. Customers will begin weighing sustained performance and battery life more heavily than peak numbers.

- Expect OEMs to split SKUs not just by core count but by tuned power curves. Two laptops with the same chip could feel very different depending on thermal design and firmware tuning.

- Edge compute devices and on-device ML stand to benefit: more capable cores at lower clocks could enable richer local inference and preprocessing tasks without expensive discrete accelerators.

What to watch next

Look for full review units and longer sustained-load tests once Medusa Point enters OEM systems. Important metrics will be: sustained multi-thread throughput, battery runtime under mixed workloads, thermal throttling curves, and integrated GPU benchmarks. Also watch firmware and driver optimizations—those often unlock the real-world potential beyond raw silicon improvements.

If these early indicators are accurate, Medusa Point could shift how we think about mobile performance: delivering similar or better real-world speed while lowering energy cost and thermal overhead. That’s a meaningful win for users, developers, and laptop designers alike.